매스웍스(kr.mathworks.com)가 매트랩(MATLAB) 및 시뮬링크(Simulink)의 최신 릴리스 2019b(R2019b)에 포함된 HDL 베리파이어(HDL Verifier)의 프로그래머블 반도체(FPGA) 및 주문형 반도체(ASIC) 설계를 위한 범용 검증 방법론(UVM)* 지원 기능을 15일 발표했다.

HDL 베리파이어는 FPGA 및 ASIC 설계 검증 담당 엔지니어가 시뮬링크를 통해 직접 UVM 컴포넌트 및 테스트 벤치를 생성하고, 시놉시스(Synopsys), 케이던스(Cadence), 멘토 그래픽스(Mentor Graphics) 등과 같이 UVM을 지원하는 시뮬레이터에서 사용할 수 있도록 지원한다.

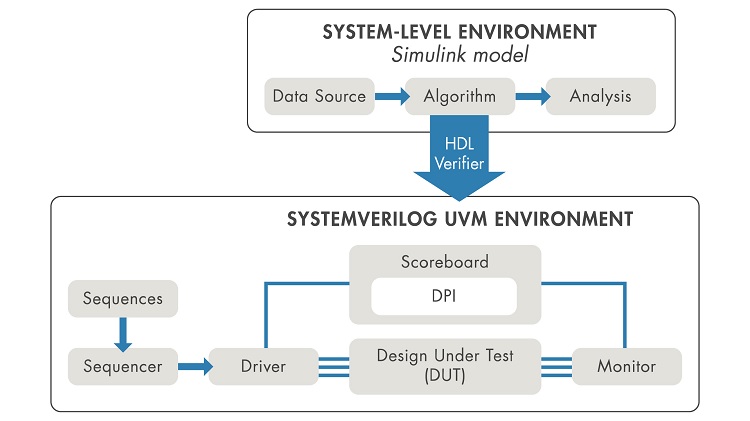

이제 설계 검증(DV) 엔지니어는 HDL 베리파이어를 통해 시뮬링크에서 이미 개발된 시스템 레벨 모델로부터 시퀀스 및 스코어보드 등의 UVM 컴포넌트를 자동 생성함으로써, 수동으로 테스트 벤치를 작성하는 데 드는 시간을 줄일 수 있게 됐다. 이러한 접근방식은 검증 엔지니어가 무선 통신, 임베디드 비전 및 제어와 같은 분야에서 ASIC 및 FPGA 설계를 위한 테스트 벤치 개발 시간을 감소시키도록 돕는다.

매트랩 및 시뮬링크에서 UVM 컴포넌트, 시스템베리로그(SystemVerilog) 어설션(assertion) 및 시스템베리로그 DPI 컴포넌트를 생성하기 위한 새로운 기능으로 무장한 HDL 베리파이어는 ASIC 및 FPGA의 프로덕션 검증을 담당하는 설계 검증팀에 대한 지원을 한층 강화했다. 기존에 설계 검증팀은 HDL 시뮬레이터를 통해 엄격한 테스트 벤치를 개발하기 위해 시스템베리로그에서 코드를 작성하는 수작업을 거쳐야 했다. 이때 HDL 베리파이어는 이러한 설계 검증팀이 기존의 매트랩 및 시뮬링크 모델로부터 직접 검증 컴포넌트를 생성하고, 해당 모델을 재사용해 프로덕션 검증 환경을 보다 신속하게 구성할 수 있도록 돕는다.

AEM_Automotive Electronics Magazine

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>