매스웍스(kr.mathworks.com)는 매트랩(MATLAB)과 시뮬링크(Simulink)의 릴리스 2019b(이하 R2019b)에 포함된 비전 HDL 툴박스(Vision HDL Toolbox)를 통해 FPGA 상에서의 HFR(High Frame Rate) 및 고해상도 영상 처리를 위한 네이티브 다중 픽셀 스트리밍을 지원한다고 발표했다.

비전 HDL 툴박스는 영상, 이미지 처리 및 FPGA 설계 엔지니어가 4K 또는 8K 영상, 240fps(frame per second, 초당 프레임 수) 이상의 고해상도 영상처리 시 시스템 동작 및 구현 간의 트레이드오프를 탐색 및 시뮬레이션하는 작업을 가속화하도록 돕는다.

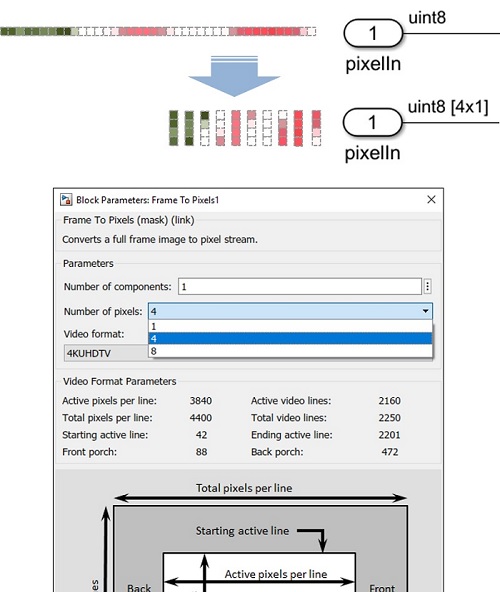

FPGA 설계 엔지니어는 산업용 검사, 의료 영상, 정보, 감시 및 정찰(ISR) 등의 애플리케이션에서 고해상도 및 HFR 영상의 실시간 처리를 구현하기 위해 처리량, 리소스 사용량 및 전력 소비량 목표를 충족시켜야 하는 도전과제에 직면해 있다. 비전 HDL 툴박스는 4 또는 8픽셀을 병렬 방식으로 처리하는 블록을 제공하며, 지정된 병렬 처리로 시뮬레이션 및 코드 생성을 수행하도록 기반 하드웨어 구현을 자동적으로 업데이트한다. 이러한 기능은 하드웨어 엔지니어가 이미지 및 영상 처리 엔지니어와 협업을 통해 높은 추상화 수준에서 비전 처리 하드웨어 동작을 탐색 및 시뮬레이션할 수 있도록 지원한다. 또한, 엔지니어는 이러한 설계 워크플로에 HDL 코더를 추가해 검증된 상위 레벨 모델로부터 직접 결합 가능하며, 타깃 독립적이고, 최적화된 VHDL 또는 Verilog 코드를 생성할 수 있다.

매스웍스의 잭 에릭슨(Jack Erickson) 수석 제품 마케팅 매니저는 “FPGA, ASIC, SoC 디바이스에서 비전 처리 알고리즘을 구현하는 데 있어서 처리량과 리소스 사용량 사이의 현명한 절충은 필수적이다. 그런데 4K, 8K, HFR 영상은 이러한 최적화를 더욱 어렵게 만든다”며 “비전 HDL 툴박스는 높은 추상화 수준에서 솔루션 공간을 탐색하고 시뮬레이션을 수행하는 기능을 통해, 엔지니어들이 RTL(Register-Transfer Level) 검증 및 확정 이전 아키텍처 상에서 보다 민첩하게 협업할 수 있도록 지원한다. 기본적으로 클록당 다중 픽셀 처리를 지원하고 모든 세부사항을 자동적으로 구현할 수 있어 엔지니어가 자사의 요구사항에 맞는 하드웨어 지원 알고리즘을 개발하는 데 보다 집중할 수 있다”고 말했다.

AEM_Automotive Electronics Magazine

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>