5년 전 Arm은 서버, 클라우드, 인프라용 CPU 코어에 대한 네오버스(Neoverse) 이니셔티브를 발표했다. 이 이니셔티브는 본격적으로 인프라 CPU 시장에 진출하기 위한 도전과 V 시리즈 코어부터 소형 E 시리즈 코어에 이르기까지 다양한 시장에 대응하기 위한 세 가지 CPU 코어 라인업을 개발하는 야심찬 다년간의 계획이었다.

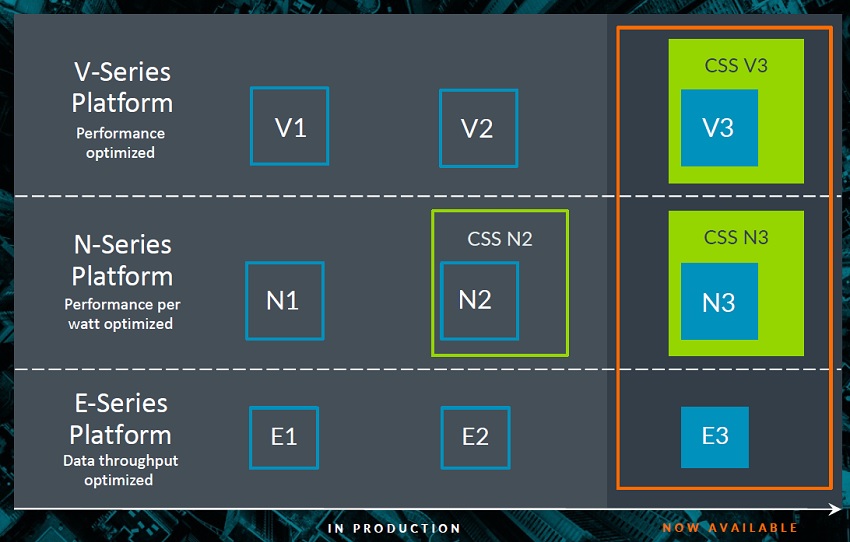

지난해 Arm은 프로세서 코어보다 더 많은 사전 검증된 구성 요소를 포함함으로써 고객이 Arm 기반 실리콘을 더 신속하게 생산할 수 있도록 지원하는 네오버스 컴퓨팅 서브시스템(Compute Sub-Systems, CSS)을 출시했다.

첫 번째 제품이 CSS N2이다. 마이크로소프트(Microsoft)는 코발트 100(Cobalt 100) 맞춤형 데이터센터 칩에, 아마존(Amazon)은 서버칩 그래비톤4(Graviton4)에 네오버스 V2 코어를 적용했다.

그리고 지난 22일, Arm은 기업이 데이터센터와 인공지능(AI)용 맞춤형 칩과 칩렛을 개발할 수 있도록 3세대 네오버스 IP 기반의 두 가지 고성능 CSS을 추가했다.

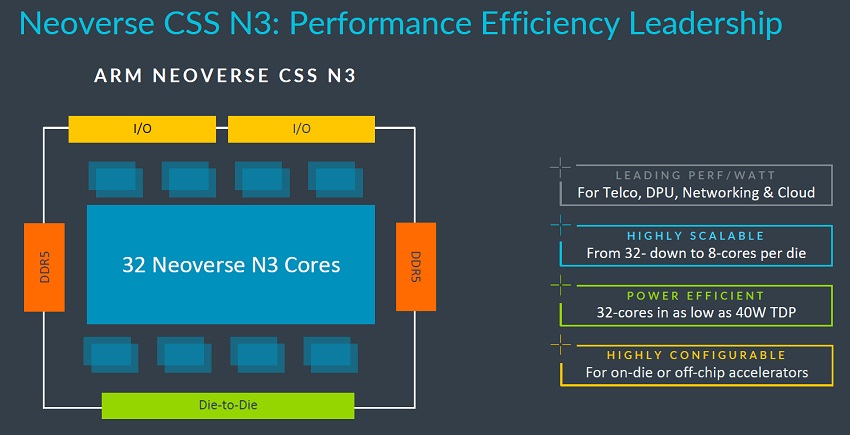

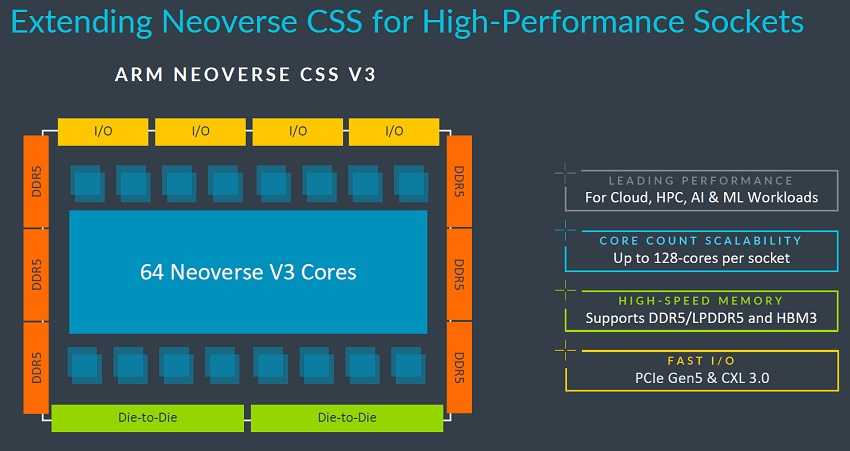

두 CSS는 전력 소비, 성능, 비용 간의 균형을 맞추기 위해 클러스터 당 최대 64개의 고성능 네오버스 V3 포세이든(Poseiden) 코어와 최대 32개의 N3 헤르메스(Hermes) 코어를 기반으로 한다. 전력 효율성에 중점을 둔 네오버스 CSS N3는 네오버스 CSS N2에 비해 와트 당 성능이 20%, 성능에 중점을 둔 네오버스 CSS V3는 이전 네오버스 CSS 제품보다 소켓 당 성능이 50% 향상되었다.

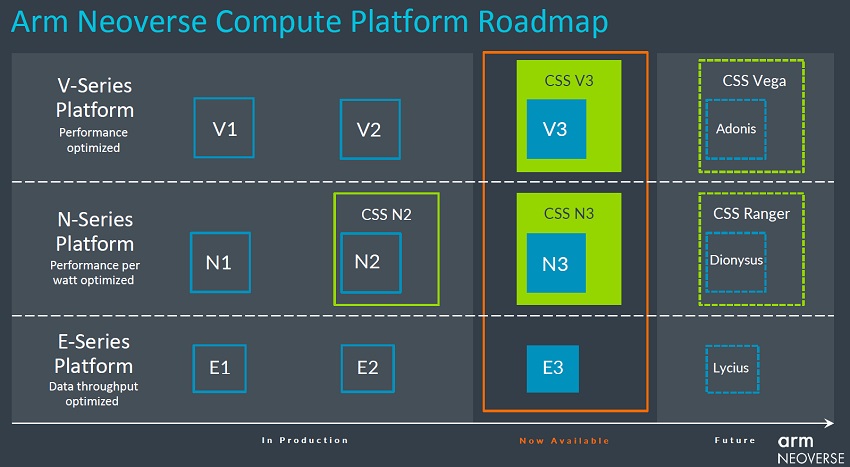

Arm은 또한 개발 중인 차세대 아도니스(Adonis) 코어를 기반으로 한 CSS 베가(Vega)와 디오니소스(Dionysus) 코어를 탑재한 CSS 레인저(Ranger)를 계획하고 있다.

네오버스 CSS V3와 N3는 V9.2 ISA(Instruction Set Architecture)를 적용한 V3 및 N3 코어를 기반으로 한 첫 번째 CSS 구현 제품이다.

둘 다 고속 인터커넥트(Interconnect) IP를 추가하여 대규모 맞춤형 칩과 칩렛을 구현하는 프레임워크에 의해 지원된다. Arm은 TSMC, 인텔, 삼성 파운드리에서 CSS V3 및 N3 설계를 사용하는 맞춤형 칩 및 칩렛 고객을 확보하고 있다고 밝혔다.

- TSMC: 소시오넥스트(Socionext Inc.) - 32 코어 네오버스 CSS V3 칩렛

- 인텔파운드리서비스(IFS): 패러데이(FARADAY) - 64 코어 N 시리즈 서버 –

- 삼성 파운드리: 에이디테크놀로지(ADTechnology) - 16 코어 N 시리즈 에지 서버

최적화에는 N3를 위한 2 MB 전용(private) L2 메모리 캐시와 데이터센터의 특정 워크로드에 대한 향상된 분기 예측 및 캐시 관리가 포함된다.

CSS N3의 가장 작은 버전은 코어가 8개이며, 대부분의 데이터센터 칩에 비해 매우 작은 40 W의 열 엔벨롭(thermal envelope)을 가지고 있다.

CSS V3는 최대 3 MB의 고속 HBM3 메모리와 PCI Express Gen5 인터커넥트를 갖춘 전용 L2 캐시가 장착된 2개의 칩으로 소켓 당 최대 128개의 코어를 지원한다. 또한, 분기 기록 버퍼 확장(Branch Record Buffer Extension, BRBE)과 같은 텔레메트리(telemetry) 기술을 제공하여 평균고장간격(Mean Time To Failure, MTBF)을 줄이고 전반적인 신뢰성을 향상시킨다.

CSS N3는 CMN S3 코히어런트 메시 네트워크, 시스템 메모리 관리 장치 MMU S3, 인터럽트 컨트롤러 NOC S3를 포함하는 네오버스 S3 시스템 IP를 기반으로 개발되었다. 또한, CSS N3는 시스템 관리 및 로컬 제어 프로세서를 포함하고 있으며, 최적화된 PPA 및 시스템 수준의 기능 지원을 위해 CPU와 시스템 IP가 공동 설계 및 공동 개발되었다.

네오버스 CSS N3는 또한 Arm의 새로운 AMBA CHI C2C 프로토콜과 함께 UCIe 다이 투 다이(Die-to-Die) 연결 표준을 지원하는 칩렛 기반 설계를 가능하게 한다. 이는 엔비디아의 그레이스 호퍼(Grace Hopper) 칩렛이 이전 네오버스 N2 코어를 사용한다는 점에서 중요하다.

N3는 다양한 컴퓨팅 시나리오에 맞는 광범위한 캐시 구성을 제공한다. 많은 스케일아웃(scale-out) 클라우드 데이터 분석 및 데이터베이스 애플리케이션은 코어에 더 가까운 대용량 캐시의 이점을 제공하므로, Arm은 2 MB L2 캐시 옵션을 추가하고 있다. 1 MB L2 캐시 옵션은 5G/6G 무선 인프라, 엔터프라이즈 네트워킹, DPU와 SmartNIC, 하이퍼스케일 서버에 이르기까지 다양한 작업에서 범용 컴퓨팅에 적합한 PPA(power, performance, and area) 균형을 제공한다. 최소 32 KB L1 및 128 KB 옵션은 캐시에 민감하지 않으면서도 적은 설치 공간에서 높은 컴퓨팅 성능을 요구하는 워크로드에 적합하다.

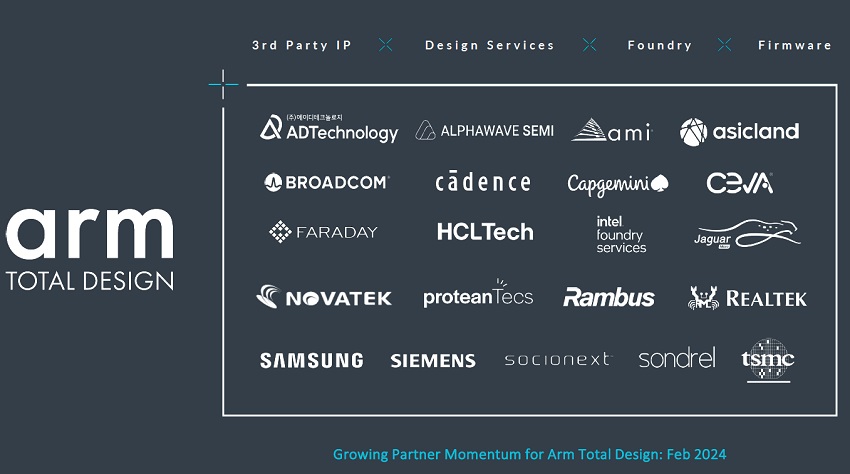

Arm은 파트너 사의 빠르고 성공적인 맞춤형 솔루션 제공을 위해 Arm Total Design을 도입했다. 이것은 네오버스 CSS를 기반으로 맞춤형 SoC를 원활하게 제공하기 위해 노력하는 파트너의 에코시스템이다. 현재 Arm Total Design 파트너 사는 20개 이상으로 확장되었다.

Arm은 최근 발표한 칩렛 시스템 아키텍처(Chiplet System Architecture, CSA)를 구체화하기 위해 Arm Total Design 에코시스템의 피드백을 활용하고 있다. CSA는 상호 교환이 가능한 칩렛 에코시스템의 모습을 정의할 예정이다.

AEM(오토모티브일렉트로닉스매거진)

<저작권자 © AEM. 무단전재 및 재배포 금지>