거리측정용 전자 시스템에는 SONAR(SOund Navigation And Ranging), RADAR(RAdio Direction And Ranging) 및 LIDAR(LIght Detection And Ranging)가 포함된다. 기본적으로 동일한 일반 원리를 이용하여 대상(목표물)과의 거리를 측정하는 이러한 시스템은 모두 에너지 소스와 반사된 신호를 탐지하여 해당 물체에 대한 여러 가지 정보를 알아낸다. 이러한 애플리케이션에서 가장 일반적인 용도는 대상까지의 거리 또는 범위를 측정하는 것이다.

RADAR는 주로 항공기와 자동차 같은 크기가 상대적으로 큰 물체를 탐지하고 모니터하는 데 사용된다. SONAR는 잠수함과 물고기 같은 수중 물체를 탐지하고 모니터하는 데 주로 사용된다. 상대적으로 새로운 기술이라고 할 수 있는 LIDAR는 측량 및 건설, 군사 범위 검색, 톨게이트에서 차량 탐지, 차량 간 거리 측정과 같은 다양한 용도로 사용된다.

[그림 1] 거리측정 시스템 블록 다이어그램

LIDAR의 최신 애플리케이션 중 하나는 자동차용 적응형 속도 제어(Adaptive Speed Control)이다. 이 애플리케이션에서 운전 제어는 다른 운전 제어 시스템에서와 마찬가지로 운전자가 원하는 속도로 설정된다. 그러나 차량이 저속으로 이동하는 차량에 접근하면 적응형 속도 제어는 안전거리를 유지하면서 차량 속도를 줄여 전방 차량과의 거리를 유지한다.

이 글은 저렴한 자동차 적응형 속도 제어 회로의 프론트엔드에 대한 원리와 설계에 대해 설명한다.

시스템 대안

이러한 시스템에서 사용할 수 있는 방법으로는 CW(Continuous Wave) 신호 또는 펄스 신호 사용이 있다.

CW 시스템은 대상이 전송된 신호의 위상 천이(Phase Shifted) 버전을 반영하는 원리에 따라 작동한다. 리시버에 있는 위상 비교기(Phase Comparator)는 수신 신호의 위상 천이 버전을 원래 신호와 비교한다. 전송 신호와 수신 신호 사이의 위상차 및 그 변화율은 거리와 거리 변화율 또는 접근율을 파악할 수 있다.

펄스형 레이저 시스템에서는 짧은 광 펄스(short light pulses)가 전송 및 수신된다. TOF(Time Of Flight)와 변화율은 대상의 위치(대상까지의 거리)와 접근율을 측정하는 데 사용된다.

이러한 모든 시스템의 경우에 DSP, FPGA 또는 마이크로컨트롤러가 처리를 위해 저속에서 데이터를 복구하여 수신 신호의 디지털화된 버전을 메모리에 전달하려면 전기 신호 소스, 전력 증폭기 및 신호를 보내는 송신기 및 수신 센서, 증폭기, 신호 컨디셔너 및 고속 ADC(Analog-to-Digital Converter)를 사용해야 한다.

자동차 애플리케이션에서 CW 시스템의 주요 단점은 시스템 비용이다. 펄스형 LASER를 사용하는 LIDAR 시스템은 훨씬 비용 효과적인 솔루션을 제공하므로 널리 사용되고 있다.

시스템 요구사항

측정할 수 있는 거리는 전송 신호의 최대 전력, 신호 분기 및 분산, 신호가 통과하는 매체의 투과율, 대상의 반사력 및 리시버 민감도를 포함한 여러 요소에 따라 다르다.

대상까지의 범위 또는 측정 가능한 최대 거리는 레이저 출력 전력, 리시버의 광 민감도, 대기가 광 에너지를 얼마나 잘 전송하는지, 레이저 빔이 완전한 직선 경로에서 얼마나 많이 분기되는지 등에 따라 달라진다.

검출기(detector)에는 리시버에서 낮은 광량(light level)을 검출하기 위해서 실리콘 PIN 검출기, 실리콘 APD(Avalanche Photo Diode), 광전자증배관(Photomultiplier tube) 등 기본적으로 세 가지가 있다. APD는 다른 검출기보다 훨씬 빠른 속도와 민감도를 가지고 있어 많은 애플리케이션에서 널리 사용되고 있다.

APD 리시버는 수신된 광 펄스를 그 빛의 양에 비례하는 전류로 변환한다. 전치증폭기(Transimpedance Amplifier, TIA)는 이 전류를 전압으로 변환한다.

아날로그 시스템에서 항상 그렇듯이, 낮은 노이즈는 신호 경로의 초기 단계에서 최상의 노이즈 성능을 요구하므로 해당 영역에서 낮은 노이즈, 높은 이득 부품을 사용해야 한다.

우수한 전치증폭기는 높은 이득, 높은 입력 임피던스, 초저 전압 및 전류 노이즈, 그리고 낮은 입력 커패시턴스를 가지고 있어야 한다. 전치증폭기의 출력은 증폭되며, ADC에 전달되어 디지털화되기 전에 추가 신호 조절이 필요할 수 있다.

수신 신호는 대개 가까운 물체에 비해 원거리에 있는 대상에 약하다. 따라서 리시버는 매우 강한 신호와 매우 약한 신호를 적절히 감지할 수 있을 정도로 민감해야 한다. 즉, 매우 넓은 시스템 동적 범위가 필요하다. 100dB 범위에서의 시스템 동적 범위 요구사항은 ADC 이전의 아날로그 VGA(Variable Gain Amplifier) 또는 DVGA(Digital Variable Gain Amplifier)을 통해 달성된다.

ADC에 차동 입력이 있는 경우, 단일 종단(Single Ended) 대 차동(Differential) 컨버터가 필요하다. ADC 이전의 마지막 단계에는 단일 종단 컨버터가 필요한 대역폭으로 충분한 이득을 제공하지 못할 경우에 사용하는 전압 증폭기가 있다. 차동 회로의 경우, 내셔널 세미컨덕터의 LMH655x 제품군이 대안이 될 수 있다.

이러한 시스템의 수신 신호 경로에서 중요한 아날로그 부품은 대상에서 반사되는 에너지를 디지털화하는 데 사용하는 ADC이다.

그림 1은 리시버의 간단한 일반 블록 다이어그램을 나타낸다. FIFO는 FPGA에 통합될 수도 있지만, ADC와 동일한 다이에 있다면 더욱 바람직하다.

ADC 요구사항

TOF 측정(거리 측정)의 정확도는 레이저의 펄스폭과 사용되는 ADC의 속도 및 정확도에 따라 다르므로 대상에서 반사된 펄스를 디지털화하는 데 사용되는 ADC는 수신 신호 경로에서 핵심적인 아날로그 부품이다.

최소 ADC 샘플링 속도는 다음과 같다.

Min fS = (c / res) 샘플/초

여기서:

fS = ADC 샘플링 속도

c = 빛의 속도

res = 거리 분해능

위의 방정식에서 "c"와 "res"는 호환 가능한 단위여야 한다. 즉 "res" 단위가 피트이면 "c" 단위는 초 당 피트가 되어야 한다.

자동차 LIDAR 시스템의 경우, 거리 측정을 위한 정확도 요구사항은 ±3피트 정도가 될 수 있다. 측정한 거리가 왕복 TOF이므로 필요한 측정 분해능은 3피트의 두 배 또는 6피트이다. 빛의 속도가 초당 299,792,458미터(일반적으로 초당 3×108터로 반올림) 또는 9.84×108피트/초라고 가정하면 최소 ADC 샘플링 속도는 다음과 같다.

Min fS = (c / res) 샘플/초

= (9.84×108 ft/sec) / 6ft

= 163.9 메가샘플/초

정상성 검사(sanity check)를 실시하여 다음과 같은 샘플 간격을 확인한다.

샘플 간격 = 1 / fS = 1 / 1.639E8 = 6.1ns.

주어진 시간에서의 왕복거리는 다음과 같다.

거리 = 신호 속도×TOF

이는 왕복거리이기 때문에 편도거리는 이 거리의 절반으로 거리 분해능과 같다.

신호 속도(빛의 속도)는 9.84×108 ft/sec이고 비행시간은 6.1 ns이다,

분해능 = 9.84×108 ft/sec×6.1×10-9 sec /2

= 3 피트

앞서 언급한 것처럼, 온칩 버퍼가 있는 ADC를 사용하는 것이 좋다. ADC08B200가 그런 제품이다. 200Msps ADC 및 1KB 온칩 버퍼를 가진 ADC08B200에는 온칩 클록 멀티플라이어도 포함되어 있어 25MHz 정도의 낮은 외부 클록 속도로 200Msps를 얻을 수 있다.

200Msps에서 ADC08B200을 사용하면 다음과 같은 왕복거리 분해능을 얻을 수 있다.

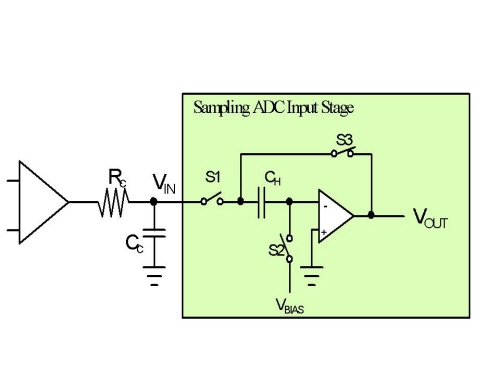

[그림 2] ADC08B200을 사용한 범위 회로

분해능 = c / fS / 2

분해능 = 9.84×108 ft/sec / 2×108 sec / 2

= 2.46 피트

LIDAR 시스템용 ADC 회로

자동차 LIDAR 리시버 설계의 핵심은 그림 2의 시스템 블록 다이어그램에서 볼 수 있듯이, 리시버 설계를 간단하게 해주는 ADC08B200에 있다. ADC08B200에는 A/D 컨버터는 물론 클록 멀티플라이어, 저렴하고 쉽게 구입할 수 있는 저주파수 클록 오실레이터, 그리고 FPGA, DSP 또는 마이크로컨트롤러의 속도 및 복잡성 요구사항을 줄여 주는 1KB 버퍼가 있다.

클록 멀티플라이어는 입력 주파수를 1, 2, 4 또는 8로 곱할 수 있다. 따라서 25MHz 정도의 낮은 클록 소스를 사용하여 200Msps 동작이 가능하다. 필요한 경우 ADC08B200의 외부 클록 소스는 FPGA/DSP/마이크로컨트롤러용 클록과 같을 수 있다.

버퍼는 최대 200MHz의 원하는 속도에서 읽을 수 있다. ADC 샘플링 속도에서 데이터가 계속 스트리밍되는 경우에는 버퍼를 무시할 수도 있다.

평균 전력 소모를 최소화하기 위해, 버퍼를 읽는 동안 ADC08B200의 ADC 코어 전력을 꺼둘 수 있다. 시스템 전력은 유지하지만 데이터 컨버터를 사용하지 않을 경우에는 버퍼를 포함한 전체 ADC08B200의 전력을 꺼둘 수도 있다.

ADC08B200 회로

그림 3에서 볼 수 있듯이, ADC08B200 주변의 회로는 간단하게 설계할 수 있다. 최상의 성능은 1V 정도의 낮은 기준전압으로 얻을 수 있으며, 기준전압을 낮게 유지하면 APD의 신호 이득 요구사항이 줄어들므로, 이 설계는 1.2V LM4041-1.2 션트 기준전압(shunt reference)을 사용하여 ADC08B200 상단(top) 기준전압을 제공하고 하단(bottom) 기준전압은 접지된다. 물론 증폭기, VGA 또는 DVGA의 최소 출력이 접지되지 않을 경우 하단 기준전압은 접지 이상으로 상승하여 이에 대응할 수 있다.

[그림 3] ADC 회로 솔루션

1.2V의 기준전압 및 145Ω의 최소 ADC 기준전압 래더(reference ladder)를 사용하여 얻을 수 있는 최대 기준전압 전류는 약 8.3mA이다. LM4041-1.2의 최대 전류는 15mA로 지정된다. ADC08B200이 없는 경우, LM4041-1.2를 통해 15mA 이상이 흐르지 않도록 설계해야 하므로 레퍼런스 풀업 레지스터는 다음과 같은 최소값을 갖는다.

(3.6V - 1.2V) / 15 mA = 240Ω

3.6V는 3.3V 전압의 최고 공차이다. 270Ω의 레지스터를 사용하면 5% 공차가 가능하다.

ADC08B200의 MULT1 입력은 높고 MULT0 입력은 낮아 50MHz CLK 입력에 4를 곱하여 200Msps를 얻는다. BSIZE0 및 BSIZE1은 둘 다 높기 때문에 1024바이트의 최대 버퍼 크기가 사용된다. 이러한 핀 사용에 대한 자세한 내용은 ADC08B200 데이터시트를 참조하기 바란다.

읽기 클록인 RCLK는 FPGA에 의해 구동되고 ADC08B200 버퍼의 데이터를 읽는 데 사용되며 ADC08B200의 DRDY 신호는 데이터를 FGPA로 래치하는 데 사용된다.

ADC08B200은 전력이 완전히 꺼지지 않으므로 PD 핀은 접지된다. 그러나 전력 소모를 최소화할 수 있어 FPGA의 PDADC 핀으로 양자화기(quantizer)의 전력 공급을 차단한다. PDADC 핀이 높으면 ADC 자체 전력은 꺼지지만 버퍼는 활성 상태를 유지하므로 읽을 수 있다.

AEM(오토모티브일렉트로닉스매거진)

<저작권자 © AEM. 무단전재 및 재배포 금지>