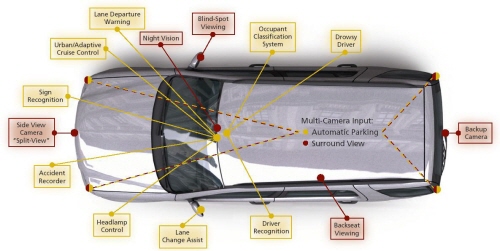

요즘 개발되고 있는 대부분의 차량 비전 시스템은 그림 1에서 보는 바와 같이 전방, 후방, 측면에 카메라를 설치하여 서로 다른 각도의 영상들의 정보를 수집한다. 응용 기술에 따라 시스템 설계자는 여러 가지 차량용 카메라 중에 적합한 카메라를 선택하게 된다. 동일 회사의 카메라 제품일지라도 서로 다른 차동 신호와 통신 프로토콜(LVDS, ITU_R BT.656, Camera Link, Digital RGB, PAL, NTSC)을 사용할 경우도 있다. 각각의 연결과 프로토콜 구조는 유효한 영상 데이터를 적당한 형태로 정형화함에 있어서 서로 다른 프로세스를 요구한다. 데이터를 전송하고 프로세싱하기 위해 전체 시스템에서 허용하는 가격 내에서 가장 최신의 디바이스를 이용하여 최고의 성능을 얻을 수 있도록 도전하고 있다.

[그림 1] 차량용 카메라 적용분야

이러한 도전에 부응하기 위해 더욱 더 많은 설계자들이 영상 처리를 위해 FPGA를 이용하여 디자인을 구현하고 있다. 왜냐하면 FPGA는 재설계가 가능하기 때문이다. FPGA는 차량 설계자들에게 최상의 성능과 유연성을 제공한다. 바로 적용할 수 있는 IP(Intellectual Property) 코어는 대부분의 업계 표준인 MPEG 디코딩/인코딩, 감마 보정(gamma correction), 컬러 분할, 스케일링, 영상 확장 및 영상 인식 등과 같은 기능 등을 설계하는 데 있어서 사용이 편리하고 디자인 일정을 단축할 수 있는 가장 좋은 방법 중에 하나다.

차량용 전자기기의 도용 방지 분야 또한 하나의 새로운 가능성을 제시한다. 개발업체의 IP, FPGA 디자인 또는 프로세서 동작 코드와 로직들은 전통적으로 복제 방지 코드가 되어 있지 않아 디자인이 쉽게 도용되고 복제되며 무허가로 조작될 수 있었다. 이런 변경에는 엔진 제어장치의 동작 파라미터를 바꾸거나 또는 내비게이션 스크린에서 DVD 영화를 볼 수 있게 하는 등의 추가적인 기능을 제공하는 것이 포함될 수 있다. 이런 변경들이 종종 차량의 중대한 결함과 동작 상의 문제 및 생명의 안전을 위협할 수 있다. 일부 FPGA는 내부에 복제 방지 코드가 내장되어 있어 도용 및 복제를 원천적으로 차단할 수 있다.

영상 처리: Distributed or Centralized?

차량용 시스템 개발자들은 항상 기능을 추가하면서도 차량의 중량을 줄이는 노력을 하고 있다. 만약, 여러 대의 카메라가 차량 주위에 부착되면 개발자들은 반드시 영상 신호의 전송에 대해 긴밀히 고려를 해야 한다. 전송 속도, 소음 제거, 무게 및 가격적인 면에서 전송매체에 대한 고려를 신중히 해야 한다.

영상 신호처리를 하는데 있어서 신중히 고려해야 할 부분은 각각의 카메라에 신호를 할당하고 원격 제어하는 부분과, 결과로 얻어진 영상 신호를 중앙의 제어장치에서 처리하고 디스플레이 될 수 있게 전송하는 분야가 있다. 몇몇 EDA 회사는 차량용 시스템 개발자들이 시스템을 분석할 수 있고 실리콘에 어떠한 기능을 구현할 것인지 또는 차량용 전송매체에 데이터를 전송하는 것들을 분석할 수 있는 개발 툴을 개발하고 있다.

분산 처리 요구사항과 예

분산된 영상 제어 프로세싱은 전자 제어 모듈에 장착되거나 신호무결성을 위해 카메라에 최대한 가까이 위치해야 한다. Micron Technology 사는 여러 개의 차량용 CMOS 영상 소자를 제공한다. MT9V111과 같은 이미지 센서는 병렬 8비트의 출력을 가지며 두 개의 동기화된 신호와 하나의 클록 신호로 이루어진다. 촬영된 영상 신호는 FPGA나 혹은 마이크로프로세서를 통해 처리된다. 각 부위에 부착된 영상기기의 제어는 적당한 차량용 전송 버스인 MOST, 1394 또는 CAN에 의해 영상 정보들을 중앙의 제어 장치로 전송한다. 이렇게 전송된 영상 신호는 알맞게 영상 신호로 조작되거나 영상 내용물의 간략한 분석을 위한 메시지로 분석된다.

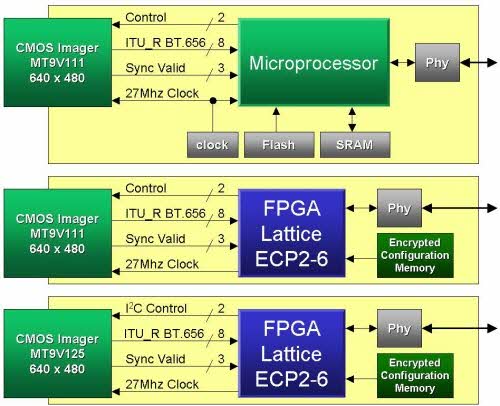

[그림 2] 분산/원격 비디오 프로세싱

3개의 분산/원격 프로세싱의 예를 그림 2에서 볼 수 있다. 첫 번째와 두 번째의 예는 MT9V111 카메라를 보여주는 데, 이 카메라는 ITU_R BT.656 또는 RGB 포맷의 8비트 병렬 출력을 가진다. 세 번째 예는 Micron MT9V125 카메라를 나타내는 데, 이 카메라는 동작 온도가 -40℃에서 +105℃에 이른다. 이 카메라는 독특한 출력 선택사양을 갖고 있다. 10B/12B LVDS, 8비트 병렬 신호와 NTSC 아날로그 신호가 선택사양으로 주어진다. 이 3가지 모든 예에서 로컬 프로세서는 신호 디코딩과 프로세싱을 위해 ITU_R BT.656 8비트 병렬 포맷의 버스로 신호를 수신한다. 추가적으로 FPGA 또는 프로세서는 CMOS 영상 소자를 위해 27MHz의 클록을 발생시키며 두 선의 시리얼 연결을 통해 영상 소자의 제어 및 카메라 내부의 저항값을 지정하여 밝기, 노출, 색보정 및 조도 등을 설정한다.

집중 처리 요구사항과 예

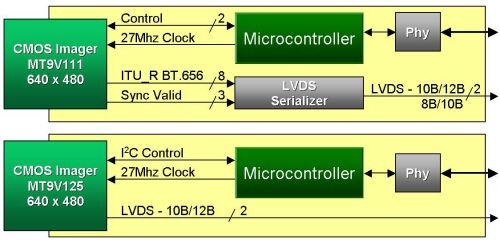

중앙 제어장치로의 카메라 영상 신호의 전송 또한 몇몇 내부 저항값을 설정하는 최소한의 정보들이 필요하다. 그림 3과 같은 예들은 저가의 마이크로컨트롤러를 사용하여 카메라의 제어와 셋팅을 한다. 또한 마이크로컨트롤러는 나머지의 차량 시스템과도 CAN이나 다른 인터페이스를 통해 통신한다. 이러한 것은 차량의 중앙 제어 장치가 마이크로컨트롤러의 구성들을 변경하면서 카메라의 셋팅이나 선택사양을 제어할 수 있게 한다.

[그림 3] 중앙처리를 위한 영상신호의 전송

첫 번째 예로서 Micron MT9V111 영상 소자는 단지 8비트의 병렬 출력만 갖고 있으며, 이는 LVDS(8B/10B 또는 10B/12B) 직렬 영상 데이터 전송을 필요로 한다. 카메라의 영상 신호들은 차동 LVDS 페어로 중앙 제어 장치로 전달된다. 이것은 AEC-Q100에 나타난 상태 기계(State machine)를 통한 제어 및 셋팅을 가능하게 하며, 이러한 로직은 크로스오버 PLD에서 구현 가능하다. 그러나 더 진보된 프로세싱이 구현되지 않는다면 마이크로컨트롤러는 가격에 영향을 미치는 주요 요소가 된다.

영상 중앙 제어 장치

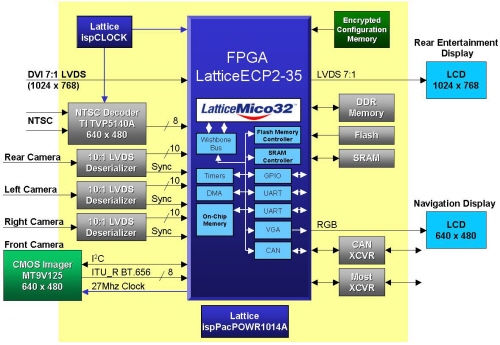

이 글에서 언급한 중앙 제어 장치는 LatticeECP2-35 FPGA이다. 이 디바이스는 3개의 분산된 카메라와 직접 연결된 카메라로부터 영상 신호를 수신한다(그림 4). 이 예는 다목적의 영상 시스템의 예로써 외부 NTSC 영상 신호와 LVDS 입력 신호를 가진다. 이것은 최종적으로 영상 데이터를 부착된 영상 화면에 보여주고 카메라 링크 LVDS 데이터를 후방의 디스플레이에 보여줄 수 있게 구성되어 있다. 이 글은 영상 애플리케이션에 중점을 두었기 때문에 음향 관련 부분은 생략한다.

다음은 그림 4에 있는 블록들의 설명이다. 블록도의 왼쪽부터 설명을 시작하겠다.

재 프로그램이 가능한 클록 제어 소자는 이 응용 부분의 모든 클록들을 제어한다. 이 소자는 FPGA의 주 클록을 생성하고 TI 사의 NTSC 영상 디코더 소자에 필요한 14.31818MHz 클록도 생성한다.

[그림 4] 중앙 영상처리 장치

첫 번째 입력은 7:1 LVDS 채널 링크 데이터이다. 이 인터페이스는 I/O 입력 블록에서 직접적으로 처리된다. 7:1 인터페이스는 영상 신호의 색심도(color depth)와 해상도에 따라 4개 또는 6개의 트위스트 쌍으로 이루어진다. 이 신호들은 DVD 플레이어로 전송되며 대역폭은 최대 75MHz까지 이른다. 추가적으로 FPGA 내부에 구성된 암호 해석 로직은 DVD 플레이어의 HDCP 프로토콜을 지원한다.

연결된 Micron CMOS 영상 소자는 27MHz 클록이 필요하다. 이 클록은 FPGA 내부에 있는 PLL을 이용하여 만들어진다.

아날로그 영상 신호 입력은 TI TVP5140V NTSC 디코더 칩을 통해 이루어지며, 이 칩은 합성 또는 단일 S-video 입력을 받는다. 출력은 8비트의 병렬 신호로 YCbCr 4:2:2의 동기 신호로 이루어진다. 이러한 연결은 외부 디바이스로부터, 예를 들어 휴대용 플레이어 또는 게임 콘솔의 입력을 가능하게 한다.

3개의 원격 카메라 입력은 차량용 기기를 설계하는 설계자들이 반드시 가격적인 면에서 고민해야 될 부분이다. 10B/12B 코딩된 영상 신호를 역직렬화(de-serialize)와 클록 복원(clock recovery)을 하기 위한 2가지 방안이 있다. 첫 번째 방법은 개별적인 10:1 LVDS 역직렬화 소자를 쓰는 것이다. 이 소자는 각각의 디자인에 2~3달러의 추가적인 비용을 요구한다. 다른 대안으로는 내부에 LVDS 신호를 디코드 할 수 있는 FPGA를 사용하는 방법이다. 하지만, 이 방법은 클록은 반드시 영상 스트림에서 클록을 추출하여야 하기 때문에 SERDES가 내장된 고가 사양의 FPGA를 사용하여야 한다.

전방(front) 카메라는 CMOS 이미지 소자가 바로 연결되며, 이 연결은 8비트 병렬 신호선으로 연결된다. 또한 카메라의 셋업이나 제어를 위해 I2C 통신 버스를 사용하고 이는 FPGA 내부 로직으로 구현할 수 있다.

FPGA 구성 메모리는 블록도의 우측 상단에 있다. 이것은 아주 작은 사이즈인 8단자 SPI 메모리이며 전원 인가 시에 FPGA에서 사용될 동작 코드를 내려준다.

소프트웨어와 IP

FPGA 내부의 로직은 2개의 부분으로 이루어진다. 개발자에 의해 디자인되는 동기/비동기 로직과 대부분의 영상 처리에 이용되는 scaling, switching, routing overlay, split-screen 등과 같은 동작을 수행하는 IP이다. 그 밖의 동작 부분은 시스템 전반을 관리하고 제어하는 로직이다. 이 부분은 LatticeMico32라는 내부 프로세스 코어와 Micrium uC/OS-II RTOS을 통해 구현된다.

Micrium의 RTOS는 FPGA 내부의 2,000개 LUT로 구현되며 MISRA(Motor Industry Software Reliability Association) C 코딩 방식과도 호환된다.

임베디드 프로세스인 LatticeMico32는 오픈소스이며 래티스 반도체가 무료로 제공하는 주변 인터페이스들을 이용할 수 있다. 주변 인터페이스로는 Timer, DMA, UART, Memory controller 등이 포함되어 있다. 이들 주변 인터페이스들은 듀얼 WISHBONE 인터페이스를 통해 프로세서 코어와 연결되어 있다. 이 디자인은 CAST5 사에서 제공하는 CAN 인터페이스 IP와 OPENCORES.org에서 제공하는 VGA 제어기를 포함하고 있다.

LatticeMico32와 uC/OS-II 소프트웨어는 로열티가 없기 때문에 차량 시스템 설계 시 인터페이스로 사용 시 무료로 사용할 수 있다.

동작 코드(Operating Code) 보안

개발자들이 차량용 애플리케이션에서 자사 IP를 보호하고 도용을 방지하기 위한 유일한 방법은 데이터 암호화 방법뿐이다. 많은 차량용 SRAM 기반의 FPGA는 부팅 디바이스와 FPGA 사이에서 개방된 구성 데이터 연결 구조를 가지는 데, 이는 허가되지 않은 사용자에 의해 FPGA에 설계된 로직을 도용이나 도난당할 수 있다. 이러한 디자인 정보는 타인에 의해 복제되거나 조작될 수 있는 환경에 노출된다. LatticeECP2 SRAM 기반의 FPGA는 개발자에게 128비트 AES 암호화 기능을 이용하여 디자인 코드를 암호화 할 수 있다. 그리고 암호화 키는 FPGA 내부에 있는 한 번만 프로그래밍 가능한 메모리에 프로그램 될 수 있다. FPGA 구성 비트스트림은 외부의 구성 메모리에 프로그램되기 전에 암호화된다. FPGA에 전원이 인가되면 이 암호화된 구성 코드가 외부 메모리에서 SPI 버스를 통해 FPGA로 다운로드된다. 이때 암호화된 코드는 내부의 키에 의해 풀리게 된다. 개발자들은 모든 기기에 같은 암호화 키를 사용하거나 더 높은 안전을 위해 각 기기의 독자적인 암호화 키를 프로그램 할 수 있다.

요약

개발자들은 차량용 비전 시스템에서 균형적인 성능 향상과 신호무결성과 무게 등을 고려하여 설계해야 하며, 이러한 것들이 양산 시 가격에 매우 민감한 부분이 될 수 있다. 정확한 카메라 또는 전송매체를 선택하면 다양한 주변 소자 및 부대 비용을 줄일 수 있다. 많은 응용분야에서 설계 시스템의 목표를 달성하기 위해 부착되고 분산되어 있는 영상 처리가 복합적으로 이루어 질 수 있다.

FPGA와 같은 프로그래밍이 가능한 소자를 이용하면 클록과 전원관리를 여러 개의 개별 소자 대신에 하나의 소자에서 구현 가능하여 시스템 단가를 줄일 뿐만 아니라 신뢰도 및 디자인 유연성도 높일 수 있다.

RTOS, 소프트 프로세서, 비디오 기능 및 통신 모듈을 위한 표준 소프트웨어와 IP를 이용하게 되면 전체 소프트웨어 개발 시간을 줄이는 데 도움이 된다.

FPGA의 부팅 코드 비트-스트림을 암호화하여 차량용 시스템 개발자들에게 개발된 차량용 비전 시스템이 외부에서 디자인 도용 또는 임의의 조작 등을 방지하는 디자인 보호를 가능하게 한다. RTOS와 프로세서 및 그것과 관련된 프로그램을 할 수 있는 메모리 등을 FPGA 내부에서 구현하면 이 디자인 또한 제조회사의 동작 코드 IP를 보호할 수 있는 방안이 된다. 소프트 프로세서 시스템은 차량용 개발자에게 기기 전반의 스케일 및 기능 설정을 가능하게 한다.

재 프로그램이 가능한 소자는 현재 차량용 비전 시스템에 필요한 디자인 보호 기능과 높은 신뢰도를 지원하며 미래의 시스템에 필요한 기능과 유연성 또한 제공한다.

Crossover PLD란?

Crossover PLD는 2006년도에 Lattice Semiconductor가 MachXO로 명명하여 출시한 새로운 프로그래머블 로직 소자군이다. 이것은 단자(pin)에서 단자까지의 지연시간이 결정가능하고 비휘발성의 FLASH와 SRAM을 사용하여 인스턴트 온 기능 및 무한의 재프로그램 기능 등을 하나의 소자에서 구현할 수 있게 했다. 이 소자군은 전통적인 큰 사이즈의 CPLD와 작은 사이즈의 FPGA 영역에 위치하며 보다 포괄적이고 가격이 저렴한 구조와 기술을 제공한다.

Directly Processing 7:1 LVDS Signals with the LatticeECP2 FPGA

여러 개의 데이터 신호들과 한 개의 클록으로 이루어지는 Source synchronous 인터페이스는 전자 시스템에서 영상 신호를 전송하는 보편적인 방법이다. 많이 사용되는 방식인 7:1 LVDS 인터페이스(Channel Link, Flat Link, Camera Link로도 알려짐)는 소비재 제품, 산업용 제어장치, 의료기기 및 차량용 텔레매틱스 등에서 널리 사용된다.

LatticeECP2에서 제공되는 특수한 입출력 구조는 7:1 LVDS 데이터를 바로 처리할 수 있는 기능을 제공한다.

위의 블록도는 7:1 LVDS 수신단이 어떻게 데이터를 처리하는 지를 보여준다. 왼쪽은 4개의 LVDS 입력 버퍼이며, 이 버퍼는 800Mbps 데이터 처리가 가능하다. 데이터 입력은 DDR 입력단과 2x Gearing을 통하여 한 클록 주기로 4개의 병렬 신호로 정렬된다. 밑의 마지막 신호는 LVDS 클록 입력이며, 이것은 내부 PLL을 통해 전달된다. 이 PLL은 내부에 필요한 클록을 재생한다. 중요한 두 개의 클록은 CLKOS에서 구동되는 ECLK(Edge Clock)과 CLKOK에서 구동되는 SCLK(System Clock)이다. CLKOS는 3.5배 채배된 클록을 90도 위상 변경시켜 입력 데이터를 안정하게 캡처할 수 있게 한다. 반면에 CLKOK는 CLKOP의 1/2 주기로 이루어져 있다. FPGA는 4비트의 데이터를 7비트의 병렬 데이터로 변환하는 4:7 de-serializer 로직이 구현되어 있다.

참고문헌

1. Micron Technology Automotive CMOS Imagers: http://www.micron.com/applications/automotive/

2. Micrium uC/OS-II Real Time Operation System: www.micrium.com

3. Lattice Semiconductor: www.latticesemi.com

4. Motor Industry Software Reliability Association: http://www.misra.org.uk

5. Cast, Inc. CAN and DUAL-CAN IP software: www.cast-inc.com

AEM(오토모티브일렉트로닉스매거진)

<저작권자 © AEM. 무단전재 및 재배포 금지>