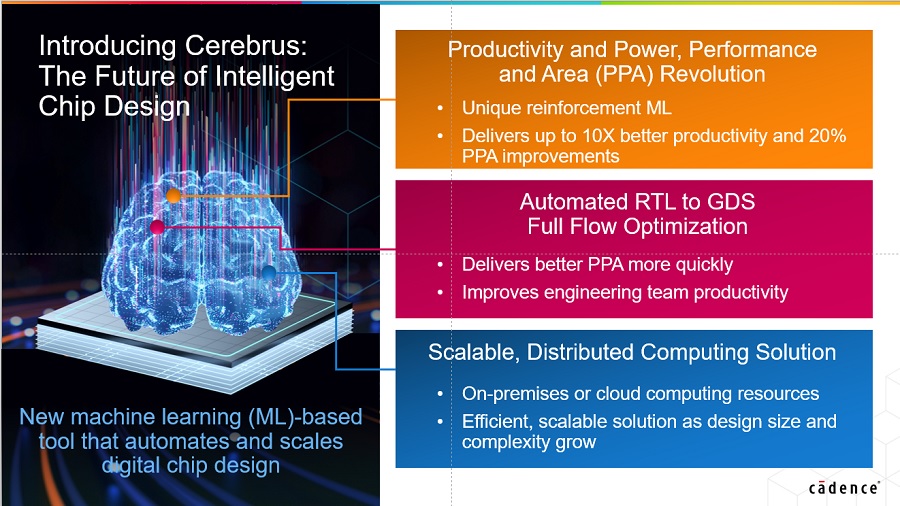

반도체설계자동화 (EDA) 툴 업체인 케이던스(Cadence Design Systems Inc.)는 디지털 칩 설계의 자동화와 효율적인 칩 설계 목표 달성을 위해 머신러닝 기반의 신제품 Cerebrus(Cadence® Cerebrus™ Intelligent Chip Explorer)를 출시했다고 2일 밝혔다.

케이던스에 따르면, Cerebrus(세레브루스)와 케이던스 시스템 반도체 사인오프(Cadence RTL-to-signoff) 플로의 조합은 칩 설계자, CAD 및 IP 개발자들이 기존에 엔지니어가 수작업으로 하던 방식에 비해 생산성을 최대 10배 향상시키고 전력과 PPA(Power Performance Area)를 최대 20%까지 개선할 수 있다.

Cerebrus는 광범위한 케이던스 디지털 풀 플로인 Genus™ 합성 솔루션, Innovus™ Auto Place & Route 구현 시스템, Tempus™ 타이밍 사인오프 솔루션, Joules™ RTL 파워 솔루션, Voltus™ IC 파워 무결성 솔루션 및 Pegasus™ 피지컬 검증 사인오프 솔루션 등과 함께 동작한다.

Cerebrus가 디지털 제품 포트폴리오에 추가되면서, 케이던스는 RTL 합성부터 구현 및 사인오프(signoff)까지 발전된 머신러닝 모델 및 디지털 풀 플로를 제공하게 됐다. 클라우드 지원이 가능한 Cerebrus는 확장성이 뛰어난 컴퓨트 리소스를 활용해 하이퍼스케일 컴퓨팅, 5G 통신, 자동차 및 모바일 등 다양한 시장의 설계 요구를 충족한다.

AEM(오토모티브일렉트로닉스매거진)

<저작권자 © AEM. 무단전재 및 재배포 금지>