Smart Vehicles Need Smart Memory Architectures: The Need for Execute-in-Place

2021-11-29 / 01월호 지면기사

/ 글 | 도니 가르시아(Donnie Garcia), 무선 MCU 제품 마케팅 매니저 조니 치엔(Johnny Chien), ISSI 플래시 제품 마케팅 매니저, NXP 반도체

.jpg)

MCU 또는 MPU가 외부 플래시를 사용해 소프트웨어를 실행하는 것을 기술 용어로 XiP(Execute in Place)라고 한다. 이 백서에서는 XiP가 자동차 산업에서 추구되는 이유와 XiP가 차량 아키텍처에 미치는 수많은 이점을 살펴본다.

글 | 도니 가르시아(Donnie Garcia), 무선 MCU 제품 마케팅 매니저

조니 치엔(Johnny Chien), ISSI 플래시 제품 마케팅 매니저, NXP 반도체

수년 동안 자동차들은 전자 부품들을 통해 더 깨끗하고 안전하고 사용자 친화적으로 변해왔다. 그리고 이제는 센싱, 컴퓨팅, 무선 연결에도 반도체 부품을 추가하며 더욱 스마트해지고 있다. 그러나 특수 소프트웨어에 의존하는 운송 목적의 마이크로컨트롤러(MCU)와 마이크로프로세서(MPU)는 여러 컴퓨터 칩에서 쉽게 휴대할 수 없으며, 이 때문에 차량 전자제품으로 사용할 수 있는 반도체 부품이 제한된다. 이것이 바로 설계를 통해 메모리 확장을 계획하는 것이 바람직한 이유 중 하나다.

MCU와 MPU 모두 중앙처리장치(CPU)가 액세스해야 하는 메모리에 저장된 기계 코드를 실행해 작동한다. 특정 프로세서가 메모리에서 소프트웨어를 실행하도록 설계하는 방법은 폐쇄형 아키텍처와 개방형 아키텍처의 두 범주로 분류될 수 있다. 일반적으로 소프트웨어는 폐쇄형 아키텍처 디바이스용 시스템 온 칩(SoC)에 내장된 메모리에서만 실행된다. 가장 단순하고 제한적인 임베디드 디바이스는 소프트웨어를 위해 통합된 비휘발성 메모리(NVM)로 구축된 MCU에 의존한다. 이와는 대조적으로 개방형 아키텍처 디바이스는 외부 구성요소를 사용해 메모리를 확장할 수 있다. MPU를 위한 주요한 메모리 아키텍처는 개방형 아키텍처이며, MCU의 경우 메모리 통합은 폐쇄형 아키텍처를 가진 전형적인 구성이다. 그러나 지난 몇 년 동안 NXP의 i.MX RT 크로스오버 MCU 시리즈를 포함한 더 많은 하이브리드 옵션이 시장에 도입됐다.

외장 메모리에는 휘발성 및 비휘발성 옵션이 있다. 휘발성 메모리의 예로는 개인용 컴퓨터나 스마트폰에 사용되는 D램이 있으며, 비휘발성 메모리 유형의 예로는 낸드(NAND) 플래시와 노어(NOR) 플래시가 있다. 노어 플래시를 사용하면 소프트웨어를 실행하는 데 필요한 빠른 랜덤 액세스가 가능하다. 노어 플래시는 견고성, 에너지 프로파일, 안정성을 통해 개방형 아키텍처 설계를 위한 NVM 옵션을 제공한다. MCU 또는 MPU가 외부 플래시를 사용해 소프트웨어를 실행하는 것을 기술 용어로 XiP(Execute in Place)라고 한다. XiP를 지원하는 MCU 또는 MPU에는 외부 노어 플래시 디바이스에서 기계 코드를 가져와 소프트웨어를 실행하는 내부 메커니즘이 포함돼 있다.

.jpg)

그림 1 | 폐쇄형 아키텍처 대 개방형 아키텍처

메모리 아키텍처의 역사

통합된 NVM에서 코드를 실행하는 폐쇄형 아키텍처는 새로운 개념이 아니다. 시장에 처음 도입된 MCU는 읽기 전용 메모리(ROM)에 구현된 NVM의 소프트웨어를 실행하는 폐쇄형 아키텍처에 기반을 두고 있는 반면, 내장형 읽기/쓰기 시스템 메모리(RAM)는 변수와 임시 데이터를 저장하는 데 사용됐다.

개방형 아키텍처를 위한 XiP는 병렬 노어 플래시가 대중화됐을 때 가장 많이 알려졌다. 내부 RAM과 플래시가 포함된 폐쇄형 아키텍처는 오늘날에도 여전히 사용되고 있지만 주로 플래시 크기가 더 작은 임베디드 시스템으로 제한된다. 일반적으로 플래시 메모리는 최신 CPU와 동일한 기술을 비용효율적으로 사용할 수 없기 때문에 개방형 아키텍처는 고성능 시스템에 최적화된다.

휴대폰과 같이 전력 소비를 제한하는 경향이 있는 애플리케이션의 경우, D램에서 대량의 코드를 실행하면 효율성이 떨어진다. 따라서 휴대폰 설계 초기에는 외장 병렬 노어 플래시 디바이스가 사용됐다. D램은 주기적으로 새로고침이 필요하기 때문에 더 많은 전력을 소비하는 경향이 있기 때문이다. 게다가 노어 플래시는 강력한 형태의 스토리지다. 노어 플래시에서 코드를 수집하고 실행하는 것은 초기에 더 적은 밀도의 D램 (휴대폰용 셀룰러 RAM 또는 PSRAM)을 필요로 했으며, 총 시스템 비용은 더욱 절감됐다.

고려해야 할 또 다른 핵심 요소는 부팅 시간이다. 많은 양의 코드를 NVM에서 D램으로 전송하고 D램에서 코드를 실행하는 데는 더 많은 시간이 필요하다. XiP는 부팅에 최소 100ms 이하의 시간이 필요한 PCI-e와 같은 특정 작업을 위해 D램에 코드를 복사하는 것에 비해 부팅 시간을 대폭 단축한다. XiP를 사용하면 D램에 코드를 전송하는 데 시간을 들이지 않고 외장 메모리에서 중요한 시스템 기능을 직접 실행할 수 있다.

노어 플래시의 XiP는 다중 레인(쿼드 또는 옥탈) 직렬 인터페이스를 도입함으로써 일반적인 임베디드 개방형 아키텍처 시스템에서 보편화됐다. 직렬 노어 플래시는 병렬 노어 플래시에 비해 상당한 핀 절감 효과를 나타내며, 컨트롤러의 핀 수를 현저하게 줄여 패키지 비용을 낮춘다.

또한 쿼드 레인 직렬 플래시는 동일한 클럭 주파수로 단일 레인보다 4배, 옥탈 레인 플래시는 최대 8배 더 빠르게 데이터를 전송할 수 있다. 그 결과, 직렬 노어 플래시는 주로 전력 및 비용 절감과 부팅 시간 단축으로 인해 일반 임베디드 시스템의 XiP 개방형 아키텍처에서 모멘텀을 가져가고 있다.

자동차 직렬 노어 플래시 XiP

엔지니어는 플래시 메모리를 데이터 스토리지로 사용하는 기존의 방식을 스마트 차량의 요구사항을 해결하는 애플리케이션으로 확장하고 있다. 이는 연결성 및 엣지 인텔리전스와 관련된 트렌드다.

오늘날의 스마트 차량은 LTE, 와이파이 카메라 및 블루투스 지원 액세스 제어를 포함하는 다수의 새로운 기능을 필요로 한다. 스마트 차량의 진화는 무선 연결을 가능하게 하는 기회와 밀접하게 엮여 있다. LTE, 와이파이 및 기타 무선 연결 옵션을 위한 표준화된 프로토콜은 메모리 요구사항과 코드를 위한 공간을 필요로 한다.

연결성과 동시에 엣지 인텔리전스와 관련된 다른 대규모 코드 크기가 필요하다. 신경망을 통한 향상된 인간-기계 인터페이스(HMI)와 고급 머신러닝을 위해서는 빠르게 액세스해야 하는 대규모 데이터 어레이가 필요하다. 이러한 요구사항은 개방형 아키텍처와 직렬 노어 플래시 디바이스의 장점과 밀접하게 일치한다.

이 백서에서는 XiP가 자동차 산업에서 추구되는 이유와 XiP가 차량 아키텍처에 미치는 수많은 이점을 살펴본다.

.jpg)

그림 2 | 연결성과 텔레매틱스

스마트 차량: 풍부한 사용자 인터페이스와 연결성

지능형 자동차 액세스 및 스마트 차량 보조 운전과 같은 새로운 기능은 XiP의 원동력이다. 또한 많은 응용 사례에 대한 지속적인 소프트웨어 개선, 연결 및 보안을 위한 시스템 통합 요구사항이 있다. 지속적인 소프트웨어 개선을 지원하기 위해 XiP 옵션으로 구축된 내장 시스템에서는 메모리 요구사항이 증가할 수 있다. 또 시스템 메모리는 강력한 펌웨어 업데이트를 위해 크기가 커지는 경우가 많으며 백업 또는 대체 이미지를 허용하기 위해 두 배로 늘어나는 경우가 많다.

연결 구현은 스마트 차량이 지원해야 하는 무선 인터페이스의 수와 유형을 증가시키고 있다. 첫째, 차량 내 사용자 경험 벡터(vector)가 있다. 휴대폰이 일상 생활에서 중심 구성요소가 됨에 따라 운전자와 승객을 와이파이 및 블루투스에 연결한다. 두 번째, 벡터는 차량 자체가 LTE 모뎀을 내장하고 온라인 모니터링 및 서비스에 직접 연결하므로 텔레매틱스(telematics)를 통해 차량이 제공하는 서비스와 관련이 있으며 상당한 코드 공간을 차지하는 소프트웨어 스택(stack)이 필요하다.

마지막으로, 내장 설계의 여러 측면에서 고려해야 하기 때문에 다른 모든 통합 요구사항을 통과하는 엄격한 보안 문제가 있다. 현재 암호화 알고리즘은 코드 크기를 늘리고 내장 시스템에 대한 추가 요구를 제기하고 있다. 하드웨어 기반 암호화가 지난 몇 년 동안 먼 길을 왔음에도 불구하고 보안 연결 설정과 관련된 프로토콜과 함께 안정성을 보장하기 위해 적용해야 하는 단계 및 절차가 여전히 필요하다. 둘 다 완전히 소프트웨어 기반 암호화 및 보안 알고리즘을 지원하거나 하드웨어 가속을 지원하는 경우 추가 코드 공간이 필요하다. 이러한 통합 요구사항으로 인해 XiP와 같은 옵션이 있는 개방형 아키텍처를 통해 메모리 확장에 대한 필요성이 높아졌다.

소프트웨어 관점에서 지속적인 개선을 지원하려면 오픈소스 커뮤니티 기반 소프트웨어 구성요소에 대한 종속성을 가진 접근 방식이 필요하다. 오픈소스는 그래픽 라이브러리, 연결 및 보안 스택에 필수적이다. 크기 최적화보다는 다양한 플랫폼에서의 작업을 강조하는 특성이 있어 메모리 확장에 대한 수요가 다시 증가하고 있다. 오픈소스에 의존하는 소프트웨어 설계 선택과 함께 주요 스마트폰 운영체제 제공업체가 제공하는 생태계와 잘 작동해야 하는 잠재적 필요성이 있다.

개방형 아키텍처의 장점

연결을 추가하거나 머신러닝을 해결하기 위해 메모리 확장이 내장 설계 전반에 걸쳐 공통적으로 필요하다는 점은 부인할 수 없다. 메모리는 XiP 기능이 있는 외부 메모리의 대안으로 장치에 내부적으로 추가될 수 있으므로 MCU/MPU에 대한 메모리 아키텍처 선택을 탐색해야 한다.

그렇다면 XiP가 포함된 개방형 아키텍처가 더 매력적인 이유는 무엇일까? 내장 시스템 설계자 관점에서 XiP의 가장 중요한 측면은 관련된 확장성이다. 외부 메모리 옵션은 성능 및 통합을 확장할 수 있고 동일한 프로세서로 처리되는 광범위한 사용 사례를 제공할 수 있기 때문이다.

또한 메인 MCU나 MPU를 교체하는 대신 더 큰 메모리나 더 빠른 메모리가 필요한 경우 외부 메모리 장치만 교체하면 된다. 외부 메모리 확장을 선택할 때 폐쇄형 아키텍처와 달리 하드웨어 및 소프트웨어 설계의 많은 측면이 제품 요구사항이 변경됨에 따라 활용된다. 예를 들어, 제조업체들은 일반적인 외부 직렬 노어 플래시 PCB footprint을 활용하여 여러 제품 스큐(skews)를 생산하거나 새로운 기능을 추가할 때 최신 메모리를 위해 Mbit에서 Gbit 범위까지 쉽게 업그레이드할 수 있으며, 개발 비용을 절감할 수 있다.

또한 시장에 나와 있는 외부 직렬 NVM 대안은 웨이퍼(wafer) 기능에 최적화될 수 있으며 내부 메모리 옵션보다 메모리의 비트당 비용을 낮출 수 있다. XiP에 의존하는 시스템은 많은 양의 메모리를 통합하는 프로세서보다 저렴할 것이다. 또한 많은 설계가 데이터 저장을 위해 직렬 노어 플래시에 의존하기 때문에 시스템에 외부 NVM이 필요한 경우 비용 효율성이 높아진다. 따라서 이러한 시스템에서 XiP를 활용하면 코드 크기 요구사항을 지원하기 위해 더 큰 메모리가 필요한 경우에만 코드 저장을 위한 추가 시스템 비용을 나타낸다. 간단히 말해서 직렬 노어 플래시가 이미 시스템에 있으므로 PCB 설계 또는 전원 관리 설계로 인한 추가 비용이 없다.

품질 및 견고성과 관련된 기능은 직렬 노어 플래시가 제공하는 최적화된 기술의 비용 이점과 함께 많은 가치를 합산한다. 직렬 노어 플래시 제품은 일반적으로 넓은 온도 범위, 긴 데이터 보존 및 풍부한 쓰기-삭제 주기를 제공한다. 또한 직렬 노어 플래시 장치는 오늘날의 프로세서보다 더 큰 지오메트리(geometry)로 제조된다. 이를 통해 직렬 노어 플래시와 같은 NVM을 자동차 설계에 필요한 열악한 환경에서 사용할 수 있다. 프로세서가 일반적으로 실리콘 웨이퍼 설계의 한계를 뛰어넘기 때문에 NVM을 통합할 수 없으며 특수 직렬 노어 플래시 장치에서 제공하는 것과 동일한 속성을 모두 유지할 수 없다.

비용, 견고성 및 시스템 확장성과 함께 XiP의 채택에 기여하는 프로세서 아키텍처 및 성능 추세가 있다. 지난 몇 년 동안 Arm에서 제공하는 것과 같은 업계 표준 CPU는 XiP의 관련 측면인 캐시(cache) 기반 시스템과 더 잘 작동하도록 아키텍처를 개선했다. 게다가 프로세서가 더 작은 제조 공정에 통합됨에 따라 관련 작동 주파수가 기가헤르츠(gigahertz) 속도로 향상되고 있다. 캐시 기반 아키텍처와 높은 CPU 속도는 메모리 인터페이스 직렬화로 인한 지연을 완화한다. 결과적으로 메모리 액세스 시간은 더 이상 내장 시스템의 성능을 좌우하는 요인이 아니다. 따라서 직렬 노어 플래시와 XiP는 오늘날의 내장 시스템에 필요한 에너지 효율성과 성능의 올바른 조합을 위한 경로를 제공한다.

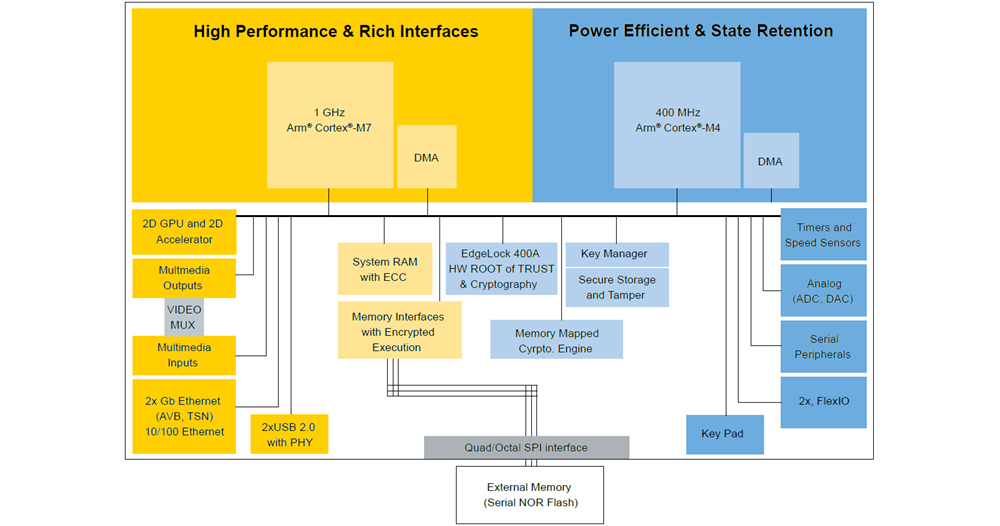

그림 3 | 프로세서 아키텍처의 예시

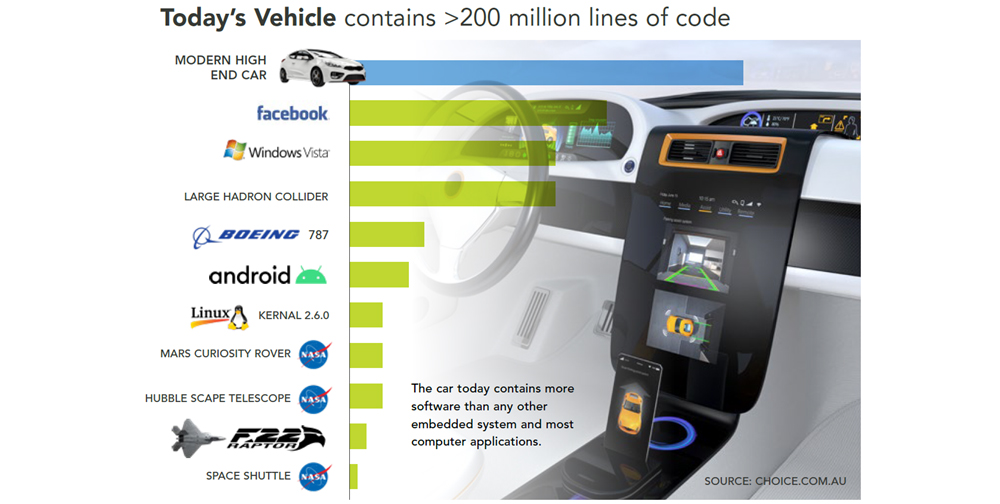

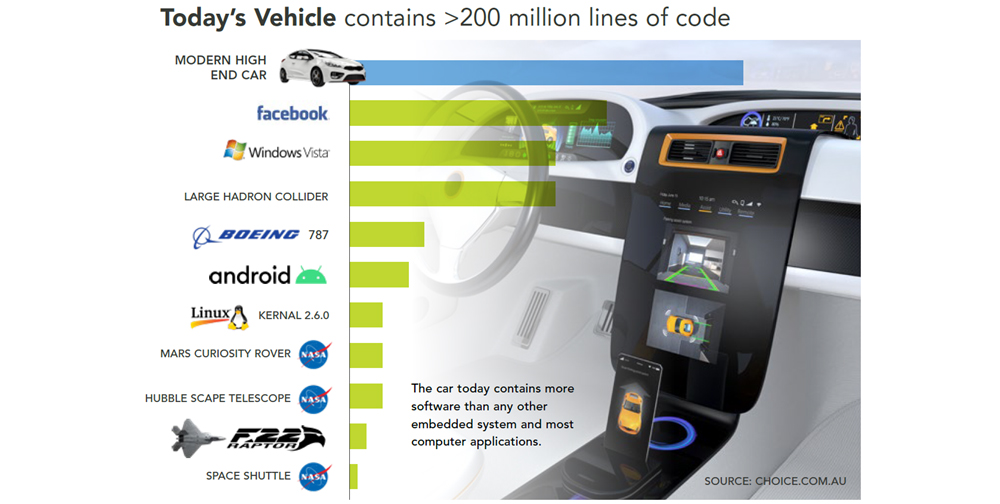

그림 4 | 최신 차량과의 코드 라인 비교

노어 플래시를 선택하는 이유

노어 플래시는 빠른 읽기 속도와 랜덤 액세스 기능을 갖춘 강력하고 안정적인 스토리지로, 특히 XiP에 적합한 코드 저장 및 실행에 이상적이다. 최근 몇 년 동안 논리 프로세스 노드(nodes)는 줄어들었지만, 플래시 프로세스 노드는 같은 속도로 감소하지 않았다. 내장 플래시 메모리는 논리 프로세스에 의해 제한된 특정 프로세스 노드 이상으로 달성하기 어렵다. 시스템이 더 복잡해짐에 따라 코드 크기가 증가하고 더 큰 코드 저장소에 대한 필요성이 플래시 메모리에 대한 외부 장치에 대한 수요를 부추겼고 결과적으로 개방형 아키텍처 메모리 서브 시스템을 빠르게 채택했다. 내장 시스템 성능과 코드 공간에 대한 필요성은 오늘날의 차량이 코드 라인의 형태로 엄청난 양의 기능을 통합해야 한다는 사실에 기인하다. 이전 그래픽에서 알 수 있듯이 실제로 차량에는 항공기, 우주선, 심지어는 운영체제보다 더 많은 코드 라인이 있다. 이러한 경향은 자동차, 산업용 애플리케이션 및 기타 분야에서 분명하다. 이는 직렬 노어 플래시 기능 및 프로세서의 발전에 대한 요구에 기여한다.

그 결과, 직렬 노어 플래시가 자연스러운 기본 값이 된 낮은 핀 수를 가진 외부 노어 플래시에 대한 필요성이 높아졌다. 한편 직렬 노어는 단일 레인 읽기에서 쿼드 및 옥탈과 같은 다중 레인 읽기 기능으로 발전했다. 이 성능 업그레이드를 통해 XiP와 그 이점인 부팅 시간 개선 외에 전력 및 비용 절감이 크게 향상됐다.

개방형 아키텍처는 추가 보안 요구사항을 요구하지만, 대부분의 자동차 애플리케이션은 추가 계층의 안정성과 성능을 기대한다. 인터그레이티드 실리콘 솔루션(Integrated Silicon Solution Inc., ISSI)는 오류 수정 코드, AX 모드 및 보안이 추가된 직렬 노어 플래시 제품군을 제공해 플래시 액세스 지침 및 기능을 최적화한다. ISSI의 직렬 노어 플래시 장치의 IS25 제품군은 이러한 요구사항을 해결할 수 있는 실용적이고 실행 가능한 솔루션을 제공한다. 모든 제품에 모든 기능이 지원되는 것은 아니다. 자세한 내용은 flash@issi.com으로 문의할 수 있다.

그림 5 | 자동차용 ISSI SPI 플래시

오류 수정 코드(Error correction code, ECC)

ISSI는 인라인 ECC 기능이 있는 직렬 노어 플래시 장치를 제공하여 표준 메모리와 역호환이 가능해 데이터 견고성과 품질을 크게 향상시키고 시스템 수준 설계를 단순화하고 전력을 절약하며 보드의 메모리 풋프린트(footprint)를 줄인다. 추가된 ECC 기능은 고신뢰성 애플리케이션, 특히 자동차 부문의 안전이 중요한 애플리케이션에 이상적이며 ISO 26262에서 정의한 필수 기능 안전을 달성하는 데 도움이 된다.

AX 읽기 모드

ISSI 직렬 노어 플래시 장치는 플래시에서 데이터를 읽기 위한 AX 읽기와 AutoBoot 모드를 제공한다. AX 읽기와 AutoBoot 모드는 빠른 실행을 위해 사용되며 임의 액세스를 위해 데이터를 출력하는 주소만 필요하다. 전원이 켜진 동안에는 AX 읽기 모드에 직접 액세스할 수 없다. 대신 AutoBoot 모드를 사용하면 시작 주소나 읽기 명령이 필요하지 않으므로 부팅 코드를 순차적으로 읽을 수 있다. 레지스터(register) 설정을 통해 미리 선택된 주소를 할당하여 시작 주소를 생략할 수 있다. AX 읽기 모드 동작은 더미 기간 동안 모드 비트(mode bits)를 적용하여 활성화된다. 모드 비트는 8비트(M7~M0)로 구성된다. 후속 읽기 실행이 M[7:4]=1010(Ah) 및 M[3:0]=X(여기서 X는 상관 없음)일 때 명령 코드를 건너뛸 때 AX 읽기 작업 활성화하고 플래시 장치는 모드 비트가 AXh와 다를 때 AX 읽기 작업을 종료한다. AutoBoot 모드와 AX 읽기 모드는 모두 오픈 아키텍처(Open Architecture) 메모리 서브 시스템의 성능을 향상시키도록 설계됐다.

보안 및 보호

ISSI는 최신의 정교한 해킹 기술에 발맞추기 위해 보안 플래시 솔루션에 대한 수요가 지속적으로 확대됨에 따라 QSPI/xSPI 플래시 장치에 내장된 주요 보안 기능을 활용하여 시스템 취약성을 해결한다. 주요 보안 기능은 다음과 같다:

BGA 패키지: 원치 않는 사용자의 악의적인 조사로부터 장치를 보호한다. BGA 패키지의 볼은 장치 바닥에 있으며 PCB에 직접 납땜 된다. 이러한 볼에 대한 흔적은 원치 않는 액세스를 방지하기 위해 다층 PCB 전체에 삽입될 수 있다. ISSI는 SPI NOR 장치를 지원하기 위해 4x6 볼 및 5x5 볼 어레이의 두 가지 유형의 24볼 TFBGA 패키지를 제공한다.

하드웨어 쓰기 금지(write-protect): USON, WSON, SOIC 및 BGA 패키지용 ISSI의 모든 SPI 플래시에 전용 WP# 핀을 제공한다. WP# 핀은 Status Register가 기록되지 않도록 보호한다. Status Register 비트에는 Quad Enable, Block Protection 및 Write Enable Latch에 대한 컨트롤이 포함되어 있다.

유일무이한 ID: ISSI에서 구현한 128비트 일련 번호를 사용하여 구성 요소 진위를 확인한다. 이 번호는 변경할 수 없지만 구성 요소 스와핑의 위협을 줄이기 위해 마이크로프로세서와 같은 다른 중요한 시스템 구성 요소와 함께 사용할 수 있다.

OTP 영역: 시스템 설계자가 메모리 배열에 해시 유형 알고리즘을 구현해 코드 신뢰성을 검증하기 위해 OTP(One Time Programmable Area)에 저장할 수 있는 원래 값을 생성할 수 있다. 시스템은 동일한 알고리즘을 사용하여 이 값을 다시 계산하고 OTP에 저장된 원래 값과 비교다. 이러한 값이 일치하지 않으면 시스템이 손상되어 문제가 해결될 때까지 후속 조치가 필요할 수 있다.

블록 보호: 사용자가 선택할 수 있는 잠금 블록을 통해 우발적이거나 악의적인 프로그래밍 및 삭제를 방지한다. 이 영역은 일시적으로 잠겨 있으며 장치에 대한 무단 변경을 방지한다.

고급 섹터 보호(Advanced Sector Protection, ASP): 휘발성 레지스터 비트(동적 보호 비트) 또는 비휘발성 레지스터 비트(영구 보호 비트)로 제어할 수 있는 개별 섹터 잠금을 허용한다. Gang Sector/Block 잠금 및 잠금 해제 명령은 모든 동적 보호 비트(Dynamic Protection Bits, DYB) 비트를 한 번에 지우거나 설정하는 빠른 방법을 제공한다. 64비트 1회 프로그래밍 가능 암호는 영구 보호 비트 (Persistent Protection Bits, PPB) 변경 사항을 추가로 보호할 수 있다.

재생 보호 모노토닉 카운터(Replay Protection Monotonic Counter, RPMC): 추가 보안을 위한 빌딩 블록을 제공하고 부트 메모리의 코드 및 데이터 저장소에 증분 단조 카운팅을 추가하여 고유성을 유지하면서 시스템이 롤백 및 재생 공격에 대한 내성을 강화하도록 돕는다.

필수 프로세서 기능

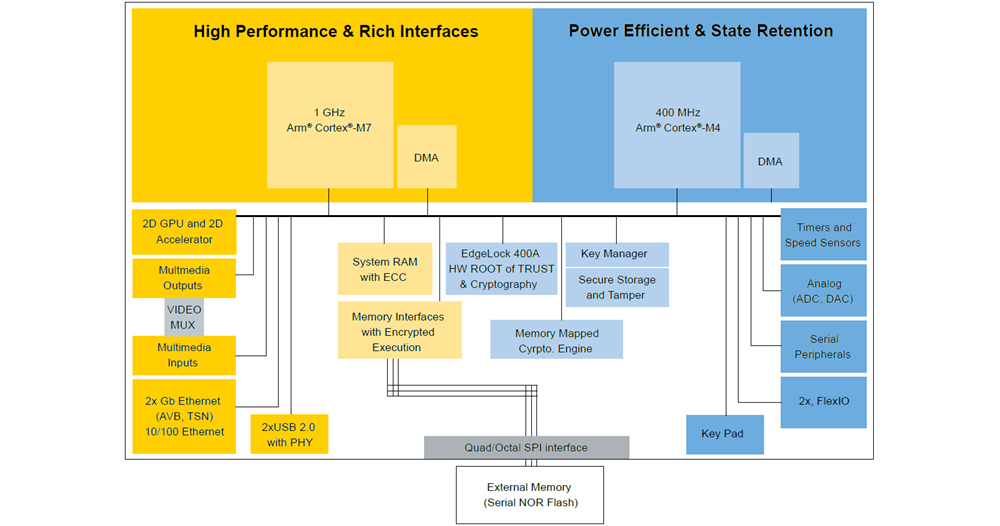

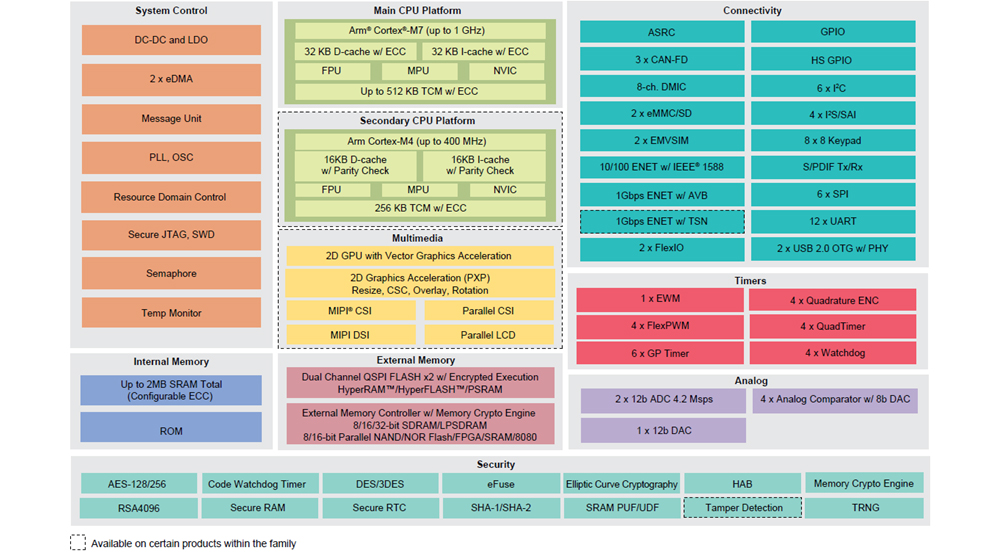

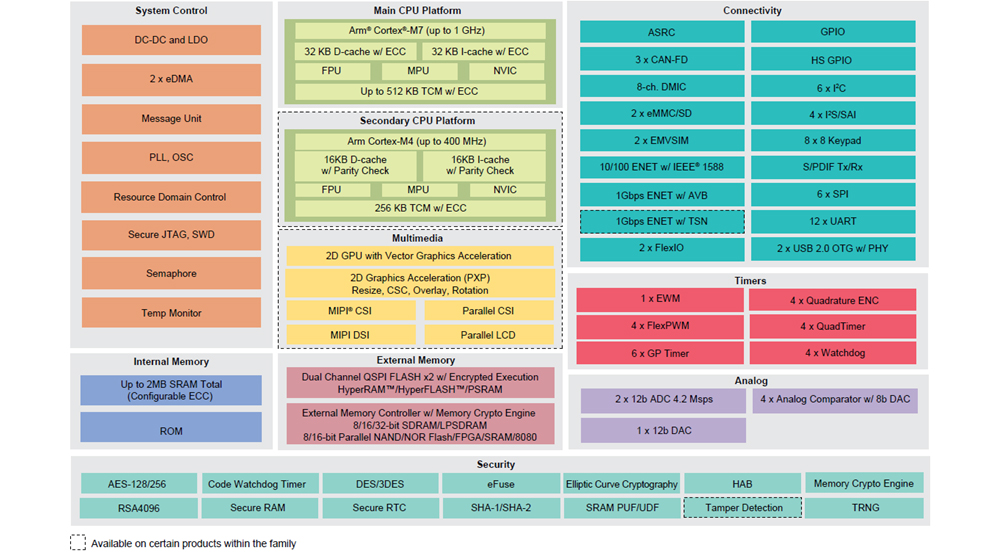

NXP는 메모리 확장의 필요성에 따라 크로스오버 마이크로컨트롤러의 전체 제품 라인을 개발했다. 최근의 한 가지 예는 고급 수준의 컴퓨팅 성능과 주변 장치를 결합한 i.MX RT1170 크로스오버 MCU이다.

그림 6 | i.MX RT1170 블록 다이어그램

그림 6 | i.MX RT1170 블록 다이어그램

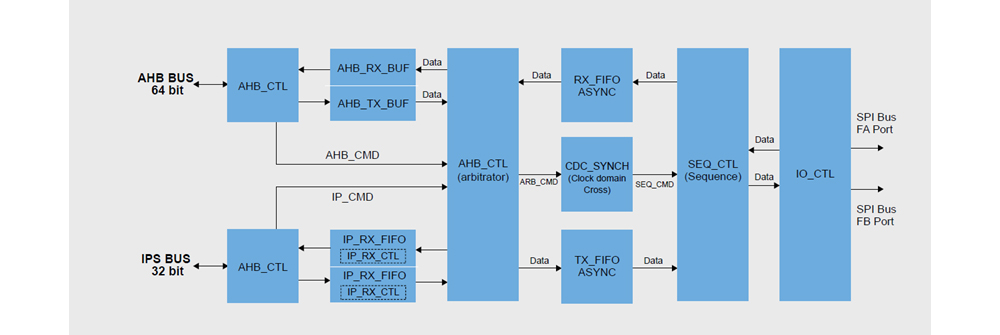

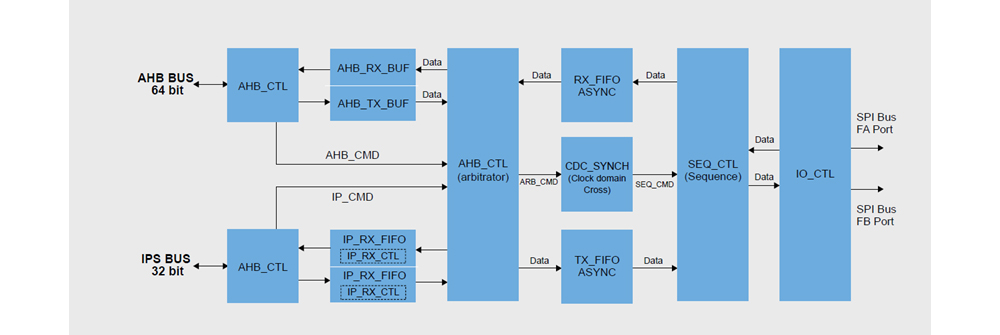

i.MX RT1170 내의 메모리 아키텍처를 통해 직렬 노어 플래시의 XiP가 기능을 보완할 수 있다. 지능형 직렬 주변기기 인터페이스(듀얼 채널 QSPI) 외부 메모리 컨트롤러와 마이크로컨트롤러 통합은 XiP 지원의 핵심이다. 이 메모리 컨트롤러 주변 장치는 표준 SPI와 같은 데이터 및 클록(clock) 신호에 의존하는 동기 직렬 프로토콜을 지원한다. 기존 SPI로 작동하는 것 외에도 이러한 향상된 주변 장치는 시스템 메모리 컨트롤러 역할을 하여 XiP 사용 사례를 더 잘 지원한다. i.MXRT1170 크로스오버 MCU에서 생성된 내부 버스 전송을 가져와 외부 메모리와 상호 작용하는 데 필요한 적절한 직렬 명령으로 변환할 수 있다. 이러한 방식으로 하드웨어는 외부 메모리에서 데이터 전송을 가속화한다. 외부 직렬 노어 플래시에 있는 명령과 데이터는 칩의 마이크로아키텍처 내부에서 발생하는 메모리 전송을 기반으로 CPU 파이프라인 또는 기타 칩 주변 장치로 직접 공급된다. 이러한 메모리 컨트롤러 중 하나는 NXP의 최신 직렬 플래시 메모리 컨트롤러인 FlexSPI이다. i.MX RT 크로스오버 프로세서는 FlexSPI 기술을 통합하고 XiP를 향상시키는 데 도움이 되며 아래 블록 다이어그램에 나와 있다.

그림 7 | FlexSPI 블록 다이어그램

그림 7 | FlexSPI 블록 다이어그램

64비트 AHB 버스는 CPU 또는 다른 온칩 마스터(LCD 컨트롤러와 같은)에서 오는 시스템 버스에 대한 인터페이스이다.

IPS BUS는 외부 인터페이스이지만 소프트웨어가 FlexSPI 레지스터 모델을 통해 노어 플래시 장치에 직접 명령을 보낼 수 있도록 한다. 이 인터페이스는 또한 명령 전송 프로세스를 시작하는 데 사용할 수 있으므로 외부 직렬 플래시를 초기화 및 구성하는 데 사용된다. AHB_CTL 블록에 연결되어 외부 메모리를 읽을 때 전송(transmit, TX) 및 수신(receive, RX) 버퍼가 데이터를 프리페치하여 XiP 작업에 대한 대기 시간과 전반적인 컴퓨팅 성능을 개선한다.

시퀀스 제어 블록(SEQ_CTL)은 읽기, 지우기 및 프로그램과 같은 다양한 직렬 플래시 작업에 대해 사전 설정된 명령을 보유하는 대형 조회 테이블이다. SEQ_CTL은 64비트 AHB 버스에서 외부 직렬 플래시로 전송되는 읽기 명령 시퀀스로의 액세스를 연결한다. 모든 플래시에 동일한 명령 세트 또는 I/O 인터페이스가 있는 것은 아니다.

시퀀스 제어 엔진은 직렬 플래시에 의해 정의된 명령 세트를 기반으로 SPI 전송을 조정하도록 프로그래밍할 수 있으므로 프로세서(예: i.MX RT1170)가 광범위한 외부 플래시 유형 및 기능과 인터페이스할 수 있다. 또한 이러한 유연성 덕분에 크로스오버 프로세서는 가장 유능한 XiP 내장 시스템을 지원하는 데 중요한 역할을 하는 플래시 속성을 활용할 수 있다.

결론

혁신적이고 유용한 기능에 대한 소비자의 요구는 자동차 공간과 전체 전자 세계에서 지속적으로 변화하여 엔지니어가 작업할 수 있는 새로운 트렌드를 만다. 더 풍부한 인간-기계 상호 작용은 내장 설계의 모든 측면에 영향을 미친다.

차량이 더 똑똑해지고 더 많은 리소스가 요구됨에 따라 메모리 아키텍처를 고려하고 확장성을 계획하는 것은 안정적이고 성공적이며 강력한 시스템에 필수적이다. 개방형 아키텍처와 제자리에서 실행(Execute-In-Place, XiP) 작동을 통해 내장 설계는 이러한 요구사항을 충족하고 설계 효율성을 보장할 수 있을 만큼 충분히 유연할 수 있다.

AEM(오토모티브일렉트로닉스매거진)

<저작권자 © AEM. 무단전재 및 재배포 금지>

.jpg)

.jpg)

.jpg)